- List of Research Specialist/Scientist/Engineer

- Update [Login required]

|

Jiang, Homin

Senior Research Engineer

|

|

|

Office: ASMAB 1017

TEL: +886-2-2366-5347

FAX: +886-2-2367-7849

Email: homin

|

Education and Positions

- Senior Research Engineer, ASIAA (2010~2018)

- Associate Research Engineer, ASIAA (2005~2010)

- Specialist, ASIAA (2001~2005)

- Megamedia Corp - DVD,ZIP,Removable harddisk, floppy; Process Automation; Control system; DVD Mastering system. (1990~2001)

- ITRI, Energy Lab. - Control system of Energy conservation Megamedia Corp (1985~1989)

- M.E., University of Iowa (1984)

Honors & Awards

- 2021 Royal Astronomical Society Group Achievement Award (2021)

- The 2020 Breakthrough Prize In Fundamental Physics. (2020)

- Albert Einstein Medal 2020. (2020)

- AAS Bruno Rossi Prize (2020)

- 2019 CTCI Foundation Science Contribution Award. (2019)

- NSF Diamond Achievement Award (2019)

Research Interests

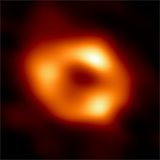

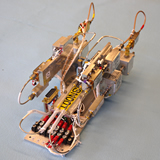

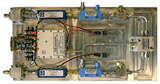

My research interests are mainly in system integration that involves software and hardware. I have developed a 5 giga sample rate ADC board for CASPER(Collaboration for Astronomy Signal Processing and Electronics Research) community, including the EHT telescope. The 5G ADC board is a part of the EHT backend system which has captured the first black hole image. In 2016-2020, I developed an even faster ADC, 16Giga sample rate that might be a candidate for the next generation EHT ADC board. I am acquiring a game-changing ADC/FPGA platform, it will have a very high ADC sampling rate. I am targeting that board for next generation GLT, LMT and other high frequency telescopes. Besides ADC development, I have been interested in the high-speed digital electronics, digital signal processing, and FPGA programming. We have built a correlator system for YTLA which is located in Mauna Loa , Hawaii. From 2020, I have been working on a beamformer/2D FFT system for BURSTT using RFSoC FPGA boards. BURSTT has 128 antennas implemented on the main site

Journal Papers affiliated with ASIAA

- Event Horizon Telescope Collaboration; Akiyama K; Alberdi A; Alef W; Algaba JC; Anantua R; Asada K; Azulay R; Bach U; Baczko A-K; Ball D; Baloković M; Bandyopadhyay B; Barrett J; Bauböck M; Benson BA; Bintley D; Blackburn L; Blundell R; Bouman KL; Bower GC; Boyce H; Bremer M; Brissenden R; Britzen S; Broderick AE; Broguiere D; Bronzwaer T; Bustamante S; Carlstrom JE; Chael A; Chan C-K; Chang DO; Chatterjee K; Chatterjee S; Chen M-T; Chen Y; Cheng X; Cho I; Christian P; Conroy NS; Conway JE; Crawford TM; Crew GB; Cruz-Osorio A; Cui Y; Dahale R; Davelaar J; De Laurentis M; Deane R; Dempsey J; Desvignes G; Dexter J; Dhruv V; Dihingia IK; Doeleman SS; Dzib SA; Eatough RP; Emami R; Falcke H; Farah J; Fish VL; Fomalont E; Ford HA; Foschi M; Fraga-Encinas R; Freeman WT; Friberg P; Fromm CM; Fuentes A; Galison P; Gammie CF; García R; Gentaz O; Georgiev B; Goddi C; Gold R; Gómez-Ruiz AI; Gómez JL; Gu M; Gurwell M; Hada K; Haggard D; Hesper R; Heumann D; Ho LC; Ho P; Honma M; Huang C-WL; Huang L; Hughes DH; Ikeda S; Violette Impellizzeri CM; Inoue M; Issaoun S; James DJ; Jannuzi BT; Janssen M; Jeter B; Jiang W; Jiménez-Rosales A; Johnson MD; Jorstad S; Jones AC; Joshi AV; Jung T; Karuppusamy R; Kawashima T; Keating GK; Kettenis M; Kim D-J; Kim J-Y; Kim J; Kim J; Kino M; Koay JY; Kocherlakota P; Kofuji Y; Koch PM; Koyama S; Kramer C; Kramer JA; Kramer M; Krichbaum TP; Kuo C-Y; La Bella N; Lee S-S; Levis A; Li Z; Lico R; Lindahl G; Lindqvist M; Lisakov M; Liu J; Liu K; Liuzzo E; Lo W-P; Lobanov AP; Loinard L; Lonsdale CJ; Lowitz AE; Lu R-S; Macdonald NR; Mao J; Marchili N; Markoff S; Marrone DP; Marscher AP; Martí-Vidal I; Matsushita S; Matthews LD; Medeiros L; Menten KM; Mizuno I; Mizuno Y; Montgomery J; Moran JM; Moriyama K; Moscibrodzka M; Mulaudzi W; Müller C; Müller H; Mus A; Musoke G; Myserlis I; Nagai H; Nagar NM; Nakamura M; Narayanan G; Natarajan I; Nathanail A; Fuentes SN; Neilsen J; Ni C; Nowak MA; Oh J; Okino H; Olivares H; Oyama T; özel F; Palumbo DCM; Paraschos GF; Park J; Parsons H; Patel N; Pen U-L; Pesce DW; Piétu V; Popstefanija A; Porth O; Prather B; Psaltis D; Pu H-Y; Ramakrishnan V; Rao R; Rawlings MG; Raymond AW; Rezzolla L; Ricarte A; Ripperda B; Roelofs F; Romero-Cañizales C; Ros E; Roshanineshat A; Rottmann H; Roy AL; Ruiz I; Ruszczyk C; Rygl KLJ; Sánchez S; Sánchez-Argüelles D; Sánchez-Portal M; Sasada M; Satapathy K; Savolainen T; Schloerb FP; Schonfeld J; Schuster K-F; Shao L; Shen Z; Small D; Sohn BW; Soohoo J; Salas LDS; Souccar K; Stanway JS; Sun H; Tazaki F; Tetarenko AJ; Tiede P; Tilanus RPJ; Titus M; Toma K; Torne P; Toscano T; Traianou E; Trent T; Trippe S; Turk M; Van Bemmel I; Van Langevelde HJ; Van Rossum DR; Vos J; Wagner J; Ward-Thompson D; Wardle J; Washington JE; Weintroub J; Wharton R; Wielgus M; Wiik K; Witzel G; Wondrak MF; Wong GN; Wu Q; Yadlapalli N; Yamaguchi P; Yfantis A; Yoon D; Young A; Younsi Z; Yu W; Yuan F; Yuan Y-F; Anton Zensus J; Zhang S; Zhao G-Y; Zhao S-S; Allardi A; Chang S-H; Chang C-C; Chang S-C; Chen C-C; Chilson R; Faber A; Gale DM; Han C-C; Han K-C; Hasegawa Y; Hernández-Rebollar JL; Huang Y-D; Jiang H; Jinchi H; Kimura K; Kubo D; Li C-T; Lin LCC; Liu C-T; Liu K-Y; Lu L-M; Martin-Cocher P; Meyer-Zhao Z; Montaña A; Moraghan A; Moreno-Nolasco ME; Nishioka H; Norton TJ; Nystrom G; Ogawa H; Oshiro P; Pradel N; Principe G; Raffin P; Rodríguez-Montoya I; Shaw P; Snow W; Sridharan TK; Srinivasan R; Wei T-S; Yu C-Y, "The persistent shadow of the supermassive black hole of M 87. I. Observations, calibration, imaging, and analysis" , A&A: 681, A79, Jan, 2024 [SCI] ( ADS | Fulltext )

- Chen M-T; Asada K; Matsushita S; Raffin P; Inoue M; Ho PTP; Han C-C; Kubo D; Norton T; Patel NA; Nystrom G; Huang C-WL; Martin-Cocher P; Koay JY; Romero-Cañizales C; Liu C-T; Huang T; Liu K-Y; Wei T; Chang S-H; Chilson R; Oshiro P; Jiang H; Li C-T; Bower G; Shaw P; Nishioka H; Koch PM; Chen C-C; Srinivasan R; Rao R; Snow W; Jinchi H; Han K-C; Chang S-C; Lu L-M; Ogawa H; Kimura K; Hasegawa Y; Pu H-Y; Koyama S; Nakamura M; Bintley D; Walther C; Friberg P; Dempsey J; Sriharan TK; Srikanth S; Doeleman SS; Brissenden R; Algaba Marcos J-C; Jeter B; Kuo C-Y; Park J, "The Greenland Telescope-Construction, Commissioning, and Operations in Pituffik" , PASP: 135 (1051), id.095001 (25 pp), Sep, 2023 [SCI] ( ADS | Fulltext )

- Lu R-S; Asada K; Krichbaum TP; Park J; Tazaki F; Pu H-Y; Nakamura M; Lobanov A; Hada K; Akiyama K; Kim J-Y; Marti-Vidal I; Gómez JL; Kawashima T; Yuan F; Ros E; Alef W; Britzen S; Bremer M; Broderick AE; Doi A; Giovannini G; Giroletti M; Ho PTP; Honma M; Hughes DH; Inoue M; Jiang W; Kino M; Koyama S; Lindqvist M; Liu J; Marscher AP; Matsushita S; Nagai H; Rottmann H; Savolainen T; Schuster K-F; Shen Z-Q; De Vicente P; Walker RC; Yang H; Zensus JA; Algaba JC; Allardi A; Bach U; Berthold R; Bintley D; Byun D-Y; Casadio C; Chang S-H; Chang C-C; Chang S-C; Chen C-C; Chen M-T; Chilson R; Chuter TC; Conway J; Crew GB; Dempsey JT; Dornbusch S; Faber A; Friberg P; García JG; Garrido MG; Han C-C; Han K-C; Hasegawa Y; Herrero-Illana R; Huang Y-D; Huang C-WL; Impellizzeri V; Jiang H; Jinchi H; Jung T; Kallunki J; Kirves P; Kimura K; Koay JY; Koch PM; Kramer C; Kraus A; Kubo D; Kuo C-Y; Li C-T; Lin LC-C; Liu C-T; Liu K-Y; Lo W-P; Lu L-M; Macdonald N; Martin-Cocher P; Messias H; Meyer-Zhao Z; Minter A; Nair DG; Nishioka H; Norton TJ; Nystrom G; Ogawa H; Oshiro P; Patel NA; Pen U-L; Pidopryhora Y; Pradel N; Raffin PA; Rao R; Ruiz I; Sanchez S; Shaw P; Snow W; Sridharan TK; Srinivasan R; Tercero B; Torne P; Traianou E; Wagner J; Walther C; Wei T-S; Yang J; Yu C-Y, "A ring-like accretion structure in M87 connecting its black hole and jet" , Nature: 616(7958), 686-690, April, 2023 [SCI] ( ADS | Fulltext )

- EHT Collaboration; Akiyama K; Alberdi A; Alef W; Algaba JC; Anantua R; Asada K; Azulay R; Bach U; Baczko A-K; Ball D; Baloković M; Barrett J; Bauböck M; Benson BA; Bintley D; Blackburn L; Blundell R; Bouman KL; Bower GC; Boyce H; Bremer M; Brinkerink CD; Brissenden R; Britzen S; Broderick AE; Broguiere D; Bronzwaer T; Bustamante S; Byun D-Y; Carlstrom JE; Ceccobello C; Chael A; Chan C-K; Chatterjee K; Chatterjee S; Chen M-T; Chen Y; Cheng X; Cho I; Christian P; Conroy NS; Conway JE; Cordes JM; Crawford TM; Crew GB; Cruz-Osorio A; Cui Y; Davelaar J; Laurentis MD; Deane R; Dempsey J; Desvignes G; Dexter J; Dhruv V; Doeleman SS; Dougal S; Dzib SA; Eatough RP; Emami R; Falcke H; Farah J; Fish VL; Fomalont E; Ford HA; Fraga-Encinas R; Freeman WT; Friberg P; Fromm CM; Fuentes A; Galison P; Gammie CF; García R; Gentaz O; Georgiev B; Goddi C; Gold R; Gómez-Ruiz AI; Gómez JL; Gu M; Gurwell M; Hada K; Haggard D; Haworth K; Hecht MH; Hesper R; Heumann D; Ho LC; Ho P; Honma M; Huang C-WL; Huang L; Hughes DH; Ikeda S; Impellizzeri CMV; Inoue M; Issaoun S; James DJ; Jannuzi BT; Janssen M; Jeter B; Jiang W; Jiménez-Rosales A; Johnson MD; Jorstad S; Joshi AV; Jung T; Karami M; Karuppusamy R; Kawashima T; Keating GK; Kettenis M; Kim D-J; Kim J-Y; Kim J; Kim J; Kino M; Koay JY; Kocherlakota P; Kofuji Y; Koch PM; Koyama S; Kramer C; Kramer M; Krichbaum TP; Kuo C-Y; Bella NL; Lauer TR; Lee D; Lee S-S; Leung PK; Levis A; Li Z; Lico R; Lindahl G; Lindqvist M; Lisakov M; Liu J; Liu K; Liuzzo E; Lo W-P; Lobanov AP; Loinard L; Lonsdale CJ; Lu R-S; Mao J; Marchili N; Markoff S; Marrone DP; Marscher AP; Martí-Vidal I; Matsushita S; Matthews LD; Medeiros L; Menten KM; Michalik D; Mizuno I; Mizuno Y; Moran JM; Moriyama K; Moscibrodzka M; Müller C; Mus A; Musoke G; Myserlis I; Nadolski A; Nagai H; Nagar NM; Nakamura M; Narayan R; Narayanan G; Natarajan I; Nathanail A; Fuentes SN; Neilsen J; Neri R; Ni C; Noutsos A; Nowak MA; Oh J; Okino H; Olivares H; Ortiz-León GN; Oyama T; özel F; Palumbo DCM; Paraschos GF; Park J; Parsons H; Patel N; Pen U-L; Pesce DW; Piétu V; Plambeck R; Popstefanija A; Porth O; Pötzl FM; Prather B; Preciado-López JA; Psaltis D; Pu H-Y; Ramakrishnan V; Rao R; Rawlings MG; Raymond AW; Rezzolla L; Ricarte A; Ripperda B; Roelofs F; Rogers A; Ros E; Romero-Cañizales C; Roshanineshat A; Rottmann H; Roy AL; Ruiz I; Ruszczyk C; Rygl KLJ; Sánchez S; Sánchez-Argüelles D; Sánchez-Portal M; Sasada M; Satapathy K; Savolainen T; Schloerb FP; Schonfeld J; Schuster K-F; Shao L; Shen Z; Small D; Sohn BW; Soohoo J; Souccar K; Sun H; Tazaki F; Tetarenko AJ; Tiede P; Tilanus RPJ; Titus M; Torne P; Traianou E; Trent T; Trippe S; Turk M; Van Bemmel I; Van Langevelde HJ; Van Rossum DR; Vos J; Wagner J; Ward-Thompson D; Wardle J; Weintroub J; Wex N; Wharton R; Wielgus M; Wiik K; Witzel G; Wondrak MF; Wong GN; Wu Q; Yamaguchi P; Yoon D; Young A; Young K; Younsi Z; Yuan F; Yuan Y-F; Zensus JA; Zhang S; Zhao G-Y; Zhao S-S; Agurto C; Allardi A; Amestica R; Araneda JP; Arriagada O; Berghuis JL; Bertarini A; Berthold R; Blanchard J; Brown K; Cárdenas M; Cantzler M; Caro P; Castillo-Domínguez E; Chan TL; Chang C-C; Chang DO; Chang S-H; Chang S-C; Chen C-C; Chilson R; Chuter TC; Ciechanowicz M; Colin-Beltran E; Coulson IM; Crowley J; Degenaar N; Dornbusch S; Durán CA; Everett WB; Faber A; Forster K; Fuchs MM; Gale DM; Geertsema G; González E; Graham D; Gueth F; Halverson NW; Han C-C; Han K-C; Hasegawa Y; Hernández-Rebollar JL; Herrera C; Herrero-Illana R; Heyminck S; Hirota A; Hoge J; Hostler Schimpf SR; Howie RE; Huang Y-D; Jiang H; Jinchi H; John D; Kimura K; Klein T; Kubo D; Kuroda J; Kwon C; Lacasse R; Laing R; Leitch EM; Li C-T; Liu C-T; Liu K-Y; Lin LCC; Lu L-M; Mac-Auliffe F; Martin-Cocher P; Matulonis C; Maute JK; Messias H; Meyer-Zhao Z; Montaña A; Montenegro-Montes F; Montgomerie W; Moreno Nolasco ME; Muders D; Nishioka H; Norton TJ; Nystrom G; Ogawa H; Olivares R; Oshiro P; Pérez-Beaupuits JP; Parra R; Phillips NM; Poirier M; Pradel N; Qiu R; Raffin PA; Rahlin AS; Ramírez J; Ressler S; Reynolds M; Rodríguez-Montoya I; Saez-Madain AF; Santana J; Shaw P; Shirkey LE; Silva KM; Snow W; Sousa D; Sridharan TK; Stahm W; Stark AA; Test J; Torstensson K; Venegas P; Walther C; Wei T-S; White C; Wieching G; Wijnands R; Wouterloot JGA; Yu C-Y; Yu W; Zeballos M, "First Sagittarius A* Event Horizon Telescope Results. I. The Shadow of the Supermassive Black Hole in the Center of the Milky Way" , ApJL: 930(2), id.L12 (21pp), May, 2022 [SCI] ( ADS | Fulltext )

- EHT Collaboration; Akiyama K; Alberdi A; Alef W; Algaba JC; Anantua R; Asada K; Azulay R; Bach U; Baczko A-K; Ball D; Baloković M; Barrett J; Bauböck M; Benson BA; Bintley D; Blackburn L; Blundell R; Bouman KL; Bower GC; Boyce H; Bremer M; Brinkerink CD; Brissenden R; Britzen S; Broderick AE; Broguiere D; Bronzwaer T; Bustamante S; Byun D-Y; Carlstrom JE; Ceccobello C; Chael A; Chan C-K; Chatterjee K; Chatterjee S; Chen M-T; Chen Y; Cheng X; Cho I; Christian P; Conroy NS; Conway JE; Cordes JM; Crawford TM; Crew GB; Cruz-Osorio A; Cui Y; Davelaar J; De Laurentis M; Deane R; Dempsey J; Desvignes G; Dexter J; Dhruv V; Doeleman SS; Dougal S; Dzib SA; Eatough RP; Emami R; Falcke H; Farah J; Fish VL; Fomalont E; Ford HA; Fraga-Encinas R; Freeman WT; Friberg P; Fromm CM; Fuentes A; Galison P; Gammie CF; García R; Gentaz O; Georgiev B; Goddi C; Gold R; Gómez-Ruiz AI; Gómez JL; Gu M; Gurwell M; Hada K; Haggard D; Haworth K; Hecht MH; Hesper R; Heumann D; Ho LC; Ho P; Honma M; Huang C-WL; Huang L; Hughes DH; Ikeda S; Impellizzeri CMV; Inoue M; Issaoun S; James DJ; Jannuzi BT; Janssen M; Jeter B; Jiang W; Jiménez-Rosales A; Johnson MD; Jorstad S; Joshi AV; Jung T; Karami M; Karuppusamy R; Kawashima T; Keating GK; Kettenis M; Kim D-J; Kim J-Y; Kim J; Kim J; Kino M; Koay JY; Kocherlakota P; Kofuji Y; Koch PM; Koyama S; Kramer C; Kramer M; Krichbaum TP; Kuo C-Y; Bella NL; Lauer TR; Lee D; Lee S-S; Leung PK; Levis A; Li Z; Lico R; Lindahl G; Lindqvist M; Lisakov M; Liu J; Liu K; Liuzzo E; Lo W-P; Lobanov AP; Loinard L; Lonsdale CJ; Lu R-S; Mao J; Marchili N; Markoff S; Marrone DP; Marscher AP; Martí-Vidal I; Matsushita S; Matthews LD; Medeiros L; Menten KM; Michalik D; Mizuno I; Mizuno Y; Moran JM; Moriyama K; Moscibrodzka M; Müller C; Mus A; Musoke G; Myserlis I; Nadolski A; Nagai H; Nagar NM; Nakamura M; Narayan R; Narayanan G; Natarajan I; Nathanail A; Fuentes SN; Neilsen J; Neri R; Ni C; Noutsos A; Nowak MA; Oh J; Okino H; Olivares H; Ortiz-León GN; Oyama T; özel F; Palumbo DCM; Paraschos GF; Park J; Parsons H; Patel N; Pen U-L; Pesce DW; Piétu V; Plambeck R; Popstefanija A; Porth O; Pötzl FM; Prather B; Preciado-López JA; Psaltis D; Pu H-Y; Ramakrishnan V; Rao R; Rawlings MG; Raymond AW; Rezzolla L; Ricarte A; Ripperda B; Roelofs F; Rogers A; Ros E; Romero-Cañizales C; Roshanineshat A; Rottmann H; Roy AL; Ruiz I; Ruszczyk C; Rygl KLJ; Sánchez S; Sánchez-Argüelles D; Sánchez-Portal M; Sasada M; Satapathy K; Savolainen T; Schloerb FP; Schonfeld J; Schuster K-F; Shao L; Shen Z; Small D; Sohn BW; Soohoo J; Souccar K; Sun H; Tazaki F; Tetarenko AJ; Tiede P; Tilanus RPJ; Titus M; Torne P; Traianou E; Trent T; Trippe S; Turk M; Van Bemmel I; Van Langevelde HJ; Van Rossum DR; Vos J; Wagner J; Ward-Thompson D; Wardle J; Weintroub J; Wex N; Wharton R; Wielgus M; Wiik K; Witzel G; Wondrak MF; Wong GN; Wu Q; Yamaguchi P; Yoon D; Young A; Young K; Younsi Z; Yuan F; Yuan Y-F; Zensus JA; Zhang S; Zhao G-Y; Zhao S-S; Agurto C; Araneda JP; Arriagada O; Bertarini A; Berthold R; Blanchard J; Brown K; Cárdenas M; Cantzler M; Caro P; Chuter TC; Ciechanowicz M; Coulson IM; Crowley J; Degenaar N; Dornbusch S; Durán CA; Forster K; Geertsema G; González E; Graham D; Gueth F; Han C-C; Herrera C; Herrero-Illana R; Heyminck S; Hoge J; Huang Y-D; Jiang H; John D; Klein T; Kubo D; Kuroda J; Kwon C; Laing R; Liu C-T; Liu K-Y; Mac-Auliffe F; Martin-Cocher P; Matulonis C; Messias H; Meyer-Zhao Z; Montenegro-Montes F; Montgomerie W; Muders D; Nishioka H; Norton TJ; Olivares R; Pérez-Beaupuits JP; Parra R; Poirier M; Pradel N; Raffin PA; Ramírez J; Reynolds M; Saez-Madain AF; Santana J; Silva KM; Sousa D; Stahm W; Torstensson K; Venegas P; Walther C; Wieching G; Wijnands R; Wouterloot JGA, "First Sagittarius A* Event Horizon Telescope Results. II. EHT and Multiwavelength Observations, Data Processing, and Calibration" , ApJL: 930(2), id.L13 (31pp), May, 2022 [SCI] ( ADS | Fulltext )

- Lin H-H; Lin K-Y; Li C-T; Tseng Y-H; Jiang H; Wang J-H; Cheng J-C; Pen U-L; Chen M-T; Chen P; Chen Y; Goto T; Hashimoto T; Hwang Y-J; King S-K; Kubo D; Kuo C-Y; Mills A; Nam J; Oshiro P; Shen C-S; Tseng H-C; Wang S-H; Feng-Shun Wu V; Bower G; Chang S-H; Chen P-A; Chen Y-C; Chiang Y-K; Fedynitch A; Gusinskaia N; Ho SCC; Hsiao TYY; Hu C-P; Huang Y D; Jauregui Garcia JM; Kim SJ; Kuo C-Y; Fang-Jie Ling D; On AYL; Peterson JB; Raquel BJR; Su S-C; Uno Y; Wu CKW; Yamasaki S; Zhu H-M, "BURSTT: Bustling Universe Radio Survey Telescope in Taiwan" , PASP: 134(1039), id.094106 (14pp), Sep, 2022 [SCI] ( ADS | Fulltext )

- Jiang H; Yu C-Y; Chen M; et al., "A Low Cost 4 bit 16 Giga-sample-per-second Analog-to-digital Converter for Radio Astronomy" , PASP: 132(1014), id.085001 (7pp.), Aug, 2020 [SCI] ( ADS | Fulltext )

- Kim J-Y; Krichbaum TP; Broderick AE; ...; Asada K; ...; Bower GC; ...; Chen MT; ...; Ho P; ...; Huang C-WL; ...; Inoue M; ...; Koay JY; Koch PM; Koyama S; ...; Kuo CY; ...; Lo WP; ...; Matsushita S; ...; Nakamura M; ...; Rao R; ...; Algaba J-C; ...; Chang C-C; Chang S-H; ...; Chen C-C; Chilson R; ...; Han C-C; ...; Huang Y-D; ...; Jiang H; ...; Kubo D; ...; Li C-T; Lin LC-C; ...; Liu K-Y; ...; Martin-Cocher PL; ...; Meyer-Zhao Z; ...; Nishioka H; ...; Nystrom G; ...; Oshiro P; ...; Pradel N; ...; Raffin PA; ...; Shaw P; ...; Snow W; ...; Srinivasan R; ...; Wei T-S; ...; Yu C-Y; et al., "Event Horizon Telescope Imaging of the Archetypal Blazar 3C 279 at an Extreme 20 Microarcsecond Resolution" , A&A: 640, id.A69 (21pp.), Aug, 2020 [SCI] ( ADS | Fulltext )

- Event Horizon Telescope Collaboration; Akiyama K; Alberdi A; ...; Asada K; ...; Bower GC; ...; Chen MT; ...; Ho PTP; ...; Huang C-W L; ...; Inoue M; ...; Koay JY; Koch PM; Koyama S; ...; Kuo C-Y; ...; Lo W-P; ...; Matsushita S; ...; Nakamura M; ...; Pen U-L; ...; Pu H-Y; ...; Rao R; ...; Algaba J-C; ...; Chang C-C; Chang S-H; Chen C-C; Chilson R; ...; Han C-C; ...; Huang Y-D;...; Jiang H; ...; Kubo D; ...; Li C-T; Lin LC-C; ...; Liu K-Y; ...; Martin-Cocher PL; ...; Meyer-Zhao Z; ...; Nishioka H; ...; Nystrom G; ...; Oshiro P; ...; Pradel N; ...; Raffin PA; ...; Shaw P; ...; Snow W; ...; Srinivasan R; ...; Wei T-S; Yu C-Y; et al., "First M87 Event Horizon Telescope Results. II. Array and Instrumentation" , ApJL: 875(1), id. L2 (28 pp.), Apr, 2019 [SCI] ( ADS | Fulltext )

- Event Horizon Telescope Collaboration; Akiyama K; Alberdi A; ...; Asada K; ...; Bower GC; Chen MT; ...; Ho PTP; ...; Huang C-W L; ...; Inoue M; ...; Koay JY; Koch PM; Koyama S; ...; Kuo C-Y; ...; Lo W-P; ...; Matsushita S; ...; Nakamura M; ...; Pen U-L; ...; Pu H-Y; ...; Rao R; ...; Algaba J-C; ...; Chang C-C; Chang S-H; Chen C-C; Chilson R; ...; Han C-C; ...; Hasegawa Y; ...; Impellizzeri CMV; ...; Hirota A; ...; Huang Y-D; ...; Jiang H; ...; Kimura K; ...; Li C-T; Lin LC-C; ...; Liu K-Y; ...; Martin-Cocher PL; ...; Meyer-Zhao Z; ...; Nishioka H; ...; Nystrom G; ...; Oshiro P; ...; Pradel N; ...; Raffin PA; ...; Shaw P; ...; Snow W; ...; Srinivasan R; ...; Wei T-S; Yu C-Y; et al., "First M87 Event Horizon Telescope Results. I. The Shadow of the Supermassive Black Hole" , ApJL: 875(1), id. L1 (17 pp.), Apr, 2019 [SCI] ( ADS | Fulltext )

- Hickish J; Abdurashidova Z; Ali Z; ...; Jiang H; .. et al., "A Decade of Developing Radio-Astronomy Instrumentation using CASPER Open-Source Technology" , JAI: 5(4), 1641001-12, Dec, 2016 ( ADS | Fulltext )

- Jiang H; Yu C-Y; Kubo D; Chen M-T; et al., "A Low-cost 4 Bit, 10 Giga-samples-per-second Analog-to-digital Converter Printed Circuit Board Assembly for FPGA-based Backends" , PASP: 128(969), 115002, Nov, 2016 [SCI] ( ADS | Fulltext )

- Lin K-Y; Nishioka H; Wang F-C; Huang C-W L; Liao Y-W; Wu J-H P; Koch PM; Umetsu K; Chen MT; ...; Chang S-H; Hoang Ngoc Duy; Han C-C; ...; Ho PTP; Huang Y-D; Jiang H; Li C-T;...; Martin-Cocher P; Molnar SM; et al., "AMiBA: Cluster Sunyaev-Zel'dovich Effect Observations with the Expanded 13-Element Array" , ApJ: 830(2), 91, Oct, 2016 [SCI] ( ADS | Fulltext )

- Inoue M; Algaba-Marcos JC; Asada K; Chang C-C; Chen M-T; Han J; Hirashita H; Ho PTP; Hsieh S-N; Huang T; Jiang H; Koch PM; Kubo DY; Kuo C-Y; Liu B; Martin-Cocher P; Matsushita S; Meyer-Zhao Z; Nakamura M; Nishioka H; Nystrom G; Pradel N; Pu H-Y; Raffin PA; Shen H-Y; Snow W; Srinivasan R; Wei T-S; Blundell R; Burgos R; Grimes P; Keto E; Paine S; Patel N; Sridharan TK; Doeleman SS; Fish V; Brisken W; Napier P, "Greenland telescope project: Direct confirmation of black hole with sub-millimeter VLBI" , Radio Science: 49(7), 564-571, July, 2014 [SCI] ( ADS | Fulltext )

- Jiang H; Liu H; Guzzino K; Kubo D; Li CT; Chang R; Chen MT, "A 5 Giga Samples Per Second 8-Bit Analog to Digital Printed Circuit Board for Radio Astronomy" , PASP: 126(942), 761-768, Aug, 2014 [SCI] ( ADS | Fulltext )

- Lin Y-C; Chou P-C; Cheng S; Jiang H ; Chen MT, "Combined Dual Plant Modeling and Controller Design with Verification for the Nutator System" , Journal of System Design and Dynamics: 5(7), 1433-1443, Nov, 2011 ( ADS | Fulltext )

- Huang CWL; ...; Ho PTP; Koch PM; ...; Lin KY; Liu GC; Molnar SM; Nishioka H; Umetsu K; ...; Altamirano P; ...; Chang CH; Chang SH; Chang SW; Chen MT; ...; Han CC; Huang YD; Hwang YJ; Jiang H; ...; Kubo D; Li CT; Martin-Cocher P; Oshiro P; Raffin P; Wei T; et al., "AMiBA: scaling relations between the integrated Compton-y and X-ray derived temperature, mass, and luminosity" , ApJ: 716(1), 758-765, June 10, 2010 [SCI] ( ADS | Fulltext )

- Li CT; Kubo DY; Wilson W; ...; Lin KY; Chen MT; Ho PTP; Chen CC; Han CC; Oshiro P; Martin-Cocher P; Chang CH; Chang SH; Altamirano P; Jiang H;...; Wang H; ...; Chang SW; Huang YD; Hwang YJ; ...; Koch P; Liu GC; Nishioka H; Umetsu K; Wei T; Wu JHP, "AMiBA Wideband Analog Correlator" , ApJ: 716(1), 746-757, June 10, 2010 [SCI] ( ADS | Fulltext )

- Liao Y-W; Wu J-HP; Ho PTP; Huang C-WL; Koch PM; Lin K-Y; Liu G-C; Molnar SM; Nishioka H; Umetsu K; Wang F-C; Altamirano P; Birkinshaw M; Chang C-H; Chang S-H; Chang S-W; Chen M-T; Chiueh T; Han C-C; Huang Y-D; Hwang Y-J; Jiang H; Kesteven M; Kubo DY; Li C-T; Martin-Cocher P;Oshiro P; Raffin P; Wei T; Wilson W, "AMiBA: Sunyaev-Zeldovich Effect Derived Properties and Scaling Relations of Massive Galaxy Clusters" , ApJ: 713(1), 584-591, APR 10 2010, 2010 [SCI] ( ADS | Fulltext )

- Liu G-C; Birkinshaw M; Wu J-HP; Ho PTP; Huang C-WL; Liao Y-W; Lin K-Y; Molnar SM; Nishioka H; Koch PM; Umetsu K; Wang F-C; Altamirano P; Chang C-H; Chang S-H; Chang S-W; Chen M-T; Han C-C; Huang Y-D; Hwang Y-J; Jiang H; Kestevan M; Kubo DY; Li C-T; Martin-Cocher P; Oshiro P; Raffin P; Wei T; Wilson W, "Contamination of the Central Sunyaev-Zel'dovich Decrements in AMiBA Galaxy Cluster Observations" , ApJ: 720(1), 608-613, Sept, 2010 [SCI] ( ADS | Fulltext )

- Chen M-T; Li C-T; Hwang Y-J; Jiang H; Altamirano P; Chang C-H; Chang S-H; Chang S-W; Chiueh T-D; Chu T-H; Han C-C; Huang Y-D; Kesteven M; Kubo D; Martin-Cocher P; Oshiro P; Raffin P; Wei T; Wang H; Wilson W; Ho PTP; Huang C-W; Koch P; Liao Y-W; Lin K-Y; Liu G-C; Molnar SM; Nishioka H; Umetsu K; Wang F-C; Wu J-HP ; et al., "AMiBA: Broadband Heterodyne CMB Interferometry" , ApJ: 694(2), 1664-1669, April 1, 2009 [SCI] ( ADS | Fulltext )

- Ho PTP; Altamirano P; Chang C-H; Chang S-H; Chang S-W; Chen C-C; Chen K-J; Chen M-T; Han C-C; Ho WM; Huang Y-D; Hwang Y-J; Ibañez-Romano F; Jiang H; Koch PM; Kubo DY; Li C-T; Lim J; Lin K-Y; Liu G-C; Lo K-Y; Ma C-J; Martin RN; Martin-Cocher P; Molnar SM; Ng K-W; Nishioka H; O'Connell KE; Oshiro P; Patt F; Raffin P; Umetsu K; Wei T; et al., "The Yuan-Tseh Lee Array for Microwave Background Anisotropy" , ApJ: 694(2), 1610-1618, April 1, 2009 [SCI] ( ADS | Fulltext )

- Koch PM; Kesteven M; Nishioka H; Jiang H; Lin K-Y; Umetsu K; Huang Y-D; Raffin P; Chen K-J; Ibañez-Romano F; Chereau G; Huang C-WL; Chen M-T; Ho PTP; Pausch K; Willmeroth K; Altamirano P; Chang C-H; Chang S-H; Chang S-W; Han C-C; Kubo D; Li C-T; Liao Y-W; Liu G-C; Martin-Cocher P; Oshiro P; Wang F-C; Wei T-S; Wu J-HP; Birkinshaw M; Chiueh T; Lancaster K; Lo KY; Martin RN; Molnar SM; et al., "The AMiBA Hexapod Telescope Mount" , ApJ: 694(2), 1670-1684, April 1, 2009 [SCI] ( ADS | Fulltext )

- Lin K-Y; Li C-T; Ho PTP; Huang C-WL; Liao Y-W; Liu G-C; Koch PM; Molnar SM; Nishioka H; Umetsu K; Wang F-C; Wu J-HP; Kestevan M; Birkinshaw M; Altamirano P; Chang C-H; Chang S-H; Chang S-W; Chen M-T; Martin-Cocher P; Han C-C; Huang Y-D; Hwang Y-J; Ibañez-Roman F; Jiang H; Kubo DY; Oshiro P; Raffin P; Wei T; Wilson W; Chen K-J; Chiueh T, "AMiBA: System Performance" , ApJ: 694(2), 1629-1636, Apr 1, 2009 [SCI] ( ADS | Fulltext )

- Nishioka H; Wang F-C; Wu J-HP; Ho PTP; Huang C-WL; Koch PM; Liao Y-W; Lin K-Y; Liu G-C; Molnar SM; Umetsu K; Birkinshaw M; Altamirano P; Chang C-H; Chang S-H; Chang S-W; Chen M-T; Han C-C; Huang Y-D; Hwang Y-J; Jiang H; Kesteven M; Kubo DY; Li C-T; Martin-Cocher P; Oshiro P; Raffin P; Wei T; Wilson W, "Tests of AMiBA Data Integrity" , ApJ: 694(2), 1637-1642, Apr 1, 2009 [SCI] ( ADS | Fulltext )

- Umetsu K; Birkinshaw M; Liu G-C; Wu J-HP; Medezinski E; Broadhurst T; Lemze D; Zitrin A; Ho PTP; Huang C-WL; Koch PM; Liao Y-W; Lin K-Y; Molnar SM; Nishioka H; Wang F-C; Altamirano P; Chang C-H; Chang S-H; Chang S-W; Chen M-T; Han C-C; Huang Y-D; Hwang Y-J; Jiang H; Kesteven M; Kubo DY; Li C-T; Martin-Cocher P; Oshiro P; Raffin P; Wei T; Wilson W, "Mass and Hot Baryons in Massive Galaxy Clusters from Subaru Weak Lensing and AMiBA Sunyaev-Zel'dovich Effect Observations" , ApJ: 694(2), 1643-1663, Apr 1, 2009 [SCI] ( ADS | Fulltext )

- Wu JHP; Ho PTP; ...; Koch PM; ...; Lin KY; Liu GC; Molnar SM; Nishioka H; Umetsu K; ...; Altamirano P; ...; Chang CH; Chang SH; Chang SW; Chen MT; ...; Han CC; Huang YD; Hwang YJ; Jiang HM; ...; Kubo DY; ...; Li CT; Martin-Cocher P; Oshiro P; Raffin P; Wei TS; et al., "Array for Microwave Background Anisotropy: Observations, Data Analysis, and Results for Sunyaev-Zel'Dovich Effects" , ApJ: 694(2), 1619-1628, Apr 1, 2009 [SCI] ( ADS | Fulltext )

- Ho PTP; Altimirano P; Birkinshaw M; Chang SW; Chang CH; Chen KJ; Chen M; Chiueh TD; Chiueh T; Chu TH; Han CC; Huang CW; Huang YD; Hwang WYP; Hwang YJ; Jiang H; Kesteven M; Koch P; Kubo D; Lancaster K; Li CT; Liang H; Liao YW; Lim J; Lin YS; Lin KY; Liu GC; Lo KY; Ma CJ; Martin-Cocher P; Martin RN; Molnar S; Ng KW; Nishioka H; Park CG; Patt F; Peterson JB; Raffin P; Romano F; Wang H; Umetsu K; Wang FC; Wu JHP, "The Yuan Tseh Lee AMiBA Project" , MPLA: 23(20), 1243-1251, June, 2008 [SCI] ( ADS | Fulltext )

- Wu J-HP; Chiueh T-H; Huang C-W; Liao Y-W; Wang F-C; Altimirano P; Chang C-H; Chang S-H; Chang S-W; Chen M-T; Chereau G; Han C-C; Ho PTP; Huang Y-D; Hwang Y-J; Jiang H; Koch P; Kubo D; Li C-T; Lin K-Y; Liu G-C; Martin-Cocher P; Molnar S; Nishioka H; Raffin P; Umetsu K; et al., "AMiBA: First-Year Results for Sunyaev-Zel'dovich Effect" , MPLA: 23(17-20), 1675-1686, June, 2008 [SCI] ( ADS | Fulltext )

- Ho PTP; Chen M-T; ...; Chiueh T; Chu T-H; Jiang H; Koch P; Kubo D; Li C-T; ...; Lin K-Y; Liu G-C; Lo K-Y; Ma C-J; Martin RN; Ng K-W; Nishioka H; Patt F; ...; Wang H; Hwang Y-J; Umetsu K; et al., "The AMiBA Project" , MPLA: 19(13-16), 993-1000, May 30, 2004 [SCI] ( ADS | Fulltext )